Im Silicon Saxony, dem deutschen Standort mit weltweit führenden Mikroelektronik und Halbleiterherstellern sowie Forschungseinrichtungen, wird tagtäglich an zukunftsweisenden Innovationen gearbeitet. Das Fraunhofer FEP, als Teil dieses eng verzahnten Netzwerkes, ist das führende Institut für die Entwicklung von kunden- und anwendungsspezifischen Mikrodisplays und Sensoren auf Basis der OLED-auf-Silizium-Technologie.

Die stetigen Mikrodisplay-Entwicklungen des Institutes in den letzten Jahren wurden getrieben durch verschiedene Anforderungen wie Pixeldichte, Energieeffizienz, Farbe, Helligkeit oder Bildrate. So entstanden am Fraunhofer FEP verschiedenste Mikrodisplays in Vollfarbe oder monochrom von ultra-low power Ausführungen bis zu hochaufgelösten Varianten für den Einsatz in Augmented (AR)- und Virtual Reality (VR)-Anwendungen und anderen Wearables.

Der überwiegende Teil der am Markt befindlichen Mikrodisplays wird derzeit auf 200 mm-Wafern in 250 nm bis zu 90 nm CMOS-Prozessknoten entwickelt und gefertigt. Auch am Fraunhofer FEP sind dies je nach Anforderung und Kundenwunsch etablierte Design-Technologien in Zusammenarbeit mit verschiedenen Halbleiterherstellern. Die Realisierung von Mikrodisplays auf 300 mm-Wafern ist bisher selten. Das ist einerseits auf technische Gründe, wie die Verfügbarkeit von passenden Transistoren für die entsprechende Ansteuerung der OLED, und andererseits auf wirtschaftliche Gründe zurückzuführen.

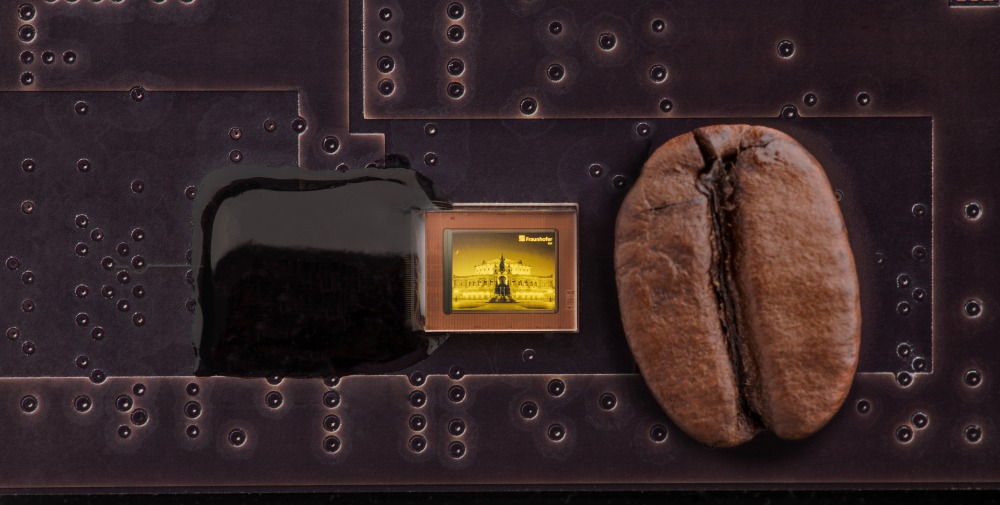

Unabhängig davon steigen jedoch die Anforderungen des Marktes an Bildqualität, Pixeldichte und integrierter Funktionalität kontinuierlich. Daher haben die Fraunhofer-Forscher im Rahmen des vom SMWA geförderten Projektes „Backplane“ die Skalierungseffekte in kleineren CMOS-Technologien betrachtet und den Einsatz von 300-mm-Backplane-Prozessen untersucht. Hierbei ist den Forschern nun der nächste große Entwicklungssprung gelungen: Sie realisierten erstmals ein OLED-Mikrodisplay mit winzigen 2,5 μm Pixeln (entsprechend 10.000 dpi) bei einer Displaydiagonale von 0,18 Zoll. Damit wurde die Machbarkeit der Entwicklung von Displays auf Basis einer 28 nm small-node-Technologie auf 300 mm Wafern gezeigt und die weltweit kleinsten Pixel eines OLED-Mikrodisplays realisiert.

Philipp Wartenberg, Abteilungsleiter für IC- und Systemdesign, erläutert zur neuen Technologie: „In kleinen Technologieknoten, sogenannten small-node-Technologien, besteht in komplexen photonischen Systemen immer die Herausforderung, die für das Treiben erforderlichen Spannungen zu realisieren. Durch ein interdisziplinäres Forschungsteam sowie eine vollkommen neuartige Display-Architektur ist uns dies im Rahmen des Projektes erstmals gelungen, wobei gleichzeitig extrem kleine Pixel mit einer Größe von lediglich 2,5 μm realisiert werden konnten. Mit diesem sehr wichtigen Entwicklungsschritt können wir unseren Kunden und Partnern zukünftig einen noch größeren Entwicklungsspielraum mit einer noch höheren Auflösung auf einer geringeren Fläche anbieten. Darüber hinaus ermöglicht die small-node-Technologie neuartige Konzepte der Ansteuerung, welche die für mobile Applikationen wichtige Stromaufnahme weiter reduziert. Dies konnten wir beispielsweise durch ein bedarfsgerechtes, flexibles Ansteuerverfahren sowie eine skalierbare Architektur zeigen.“

Die neu entwickelten OLED-Mikrodisplays haben eine Auflösung von 1440 x 1080 Pixel in monochromer Ausführung bzw. 720 x 540 Pixel in Vollfarbe. Die flexible Displayarchitektur erlaubt einerseits bei unveränderlichem Displayinhalt die Bildwiederholrate im Extremfall auf 0 Hz zu reduzieren und so sämtlichen unnötigen Datentransfer zu vermeiden – ein enormer Vorteil für die Stromaufnahme. Herkömmliche Displays benötigen hier inhaltsunabhängig eine minimale Bildwiederholrate. Andererseits erlaubt das neue Mikrodisplay im Extremfall auch Bildwiederholraten von bis zu 480 Hz – intern sogar bis zu mehreren kHz. Ermöglicht wird dies durch eine programmierbare Ablaufsteuerung in Kombination mit einem Display-integrierten Framebuffer.

Zum Einsatz kommen können die neuen Displays je nach Ausführung in Lifestyle-Produkten, wie Sportbrillen oder als Head-Mounted-Displays in Motorradhelmen, in industriellen Szenarien für Wearables in der Logistik oder für Remote-Wartungslösungen. Die jetzt noch kleineren Abmessungen ebnen den Weg in noch ergonomischere Systeme.

Die neuen OLED-Mikrodisplays werden seitens des Fraunhofer FEP als Evaluations-Kits angeboten, um interessierten Kunden Zugang und Testmöglichkeiten für die eigene Systemintegration zu bieten und gemeinsame kundenspezifische Mikrodisplayentwicklungen mit der Industrie zu ermöglichen. Auf der SID Display Week 2023, vom 23.–25. Mai 2023, in Los Angeles, USA, wurden sie zudem erstmals live auf dem Deutschen Gemeinschaftsstand beim Fraunhofer FEP und in weiteren Vorträgen präsentiert.

Über das Projekt Backplane

Backplane – Deep-submicron CMOS-Prozesstechnologie für Ansteuerung von integrierten Mikrodisplays und Auswerteschaltungen von optischen Sensoren

Fördergeber: Sächsisches Staatsministerium für Wirtschaft, Arbeit und Verkehr

Förderkennzeichen: 100392259

Laufzeit: 31.12.2019 – 31.10.2022