The collaboration has been first focused on the processing and electrical characterization of hafnium-zirconium oxide (HZO) ferroelectric capacitor stacks. Utilizing the combined 300 mm CMOS cleanroom capabilities of both institutes, the wafers were circulated in short process loops to enable joint evaluation of materials, electrode configurations, and device behavior.

The work also validated the wafer exchange and contamination-control protocols implemented in the Pilot Line, demonstrating that complex material stacks can be processed reliably across multiple advanced semiconductor facilities, on all wafers.

The entire process adhered to standardized contamination control procedures, verified through VPD-ICP-MS (Vapor Phase Decomposition – Inductively Coupled Plasma Mass Spectrometry) and TXRF (Total Reflection X-Ray Fluorescence) analytics. Devices were evaluated using a FeCAP array test vehicle designed by CEA-Leti, with electrical characterization performed via the PUND (Positive-Up-Negative-Down) methodology to isolate true ferroelectric switching from parasitic effects.

Accelerating the Path Toward System-Level Application

“The successful wafer exchange marks an important step toward a joint European material testing platform for ferroelectric memories,” said Dr. Wenke Weinreich, Division Director of Fraunhofer IPMS’ Center Nanoelectronic Technologies, a member of the 11-member consortium. “By combining our processing expertise with CEA-Leti’s CMOS integration capabilities, the pilot line provides a powerful environment for evaluating new ferroelectric stacks and accelerating their path toward system-level applications.”

Initial experimental results have already yielded critical insights. The team screened various electrode materials to enhance performance, finding that titanium nitride (TiN) bottom electrodes significantly outperform tungsten (W). In reliability tests, TiN exhibited lower failure rates after 10⁷ field cycles at 4 MV/cm. Furthermore, clear cross-split effects were observed across different electrode configurations, confirming the sensitivity of the test vehicles to process variations.

Seamless Exchanges Across FAMES’ Sites

“This first exchange between CEA-Leti and Fraunhofer IPMS demonstrates that shared process flows, test vehicles, and characterization environments can work seamlessly across FAMES’ sites,” noted project Coordinator Dominique Noguet. “Establishing reliable wafer loops between leading research fabs is essential for accelerating ferroelectric memory development.”

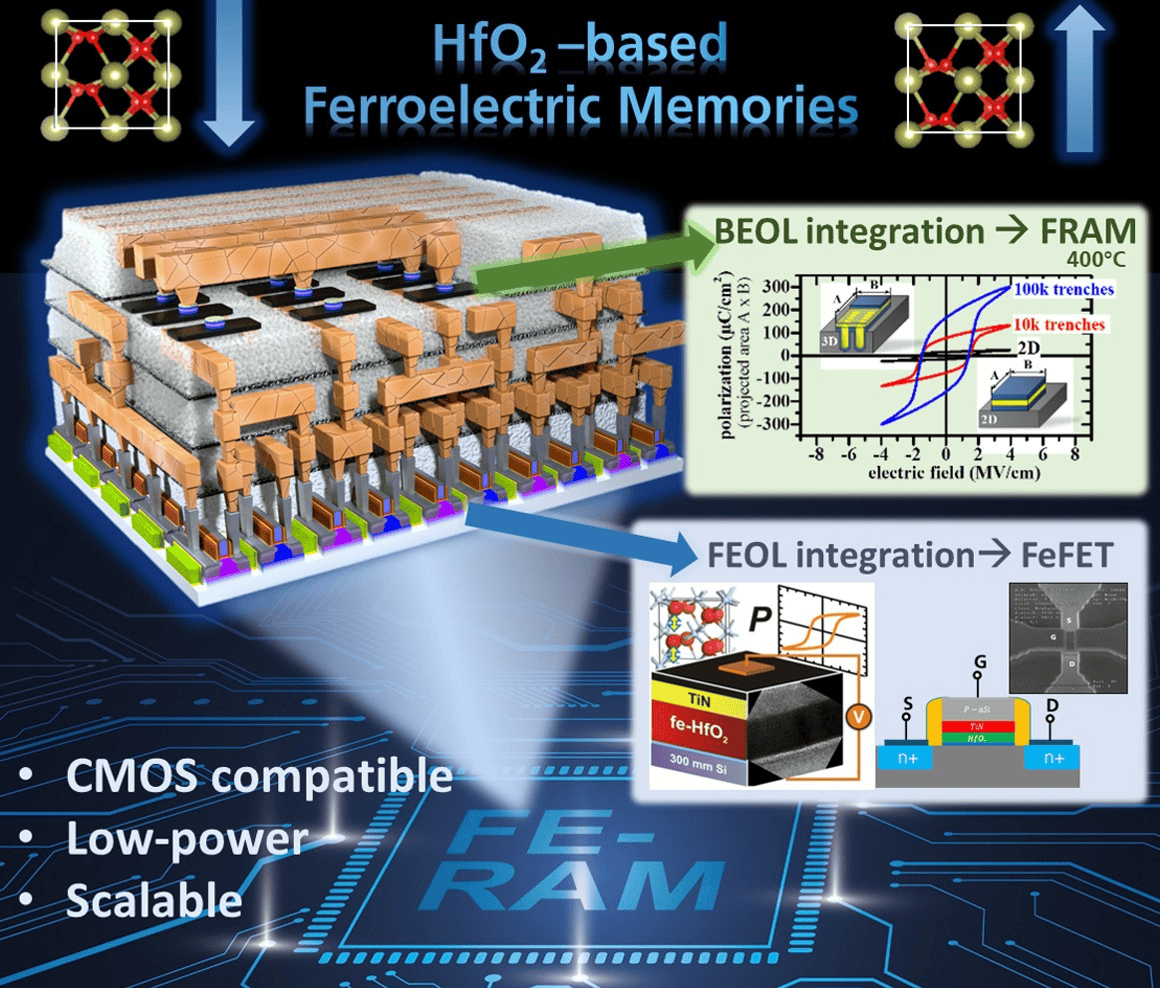

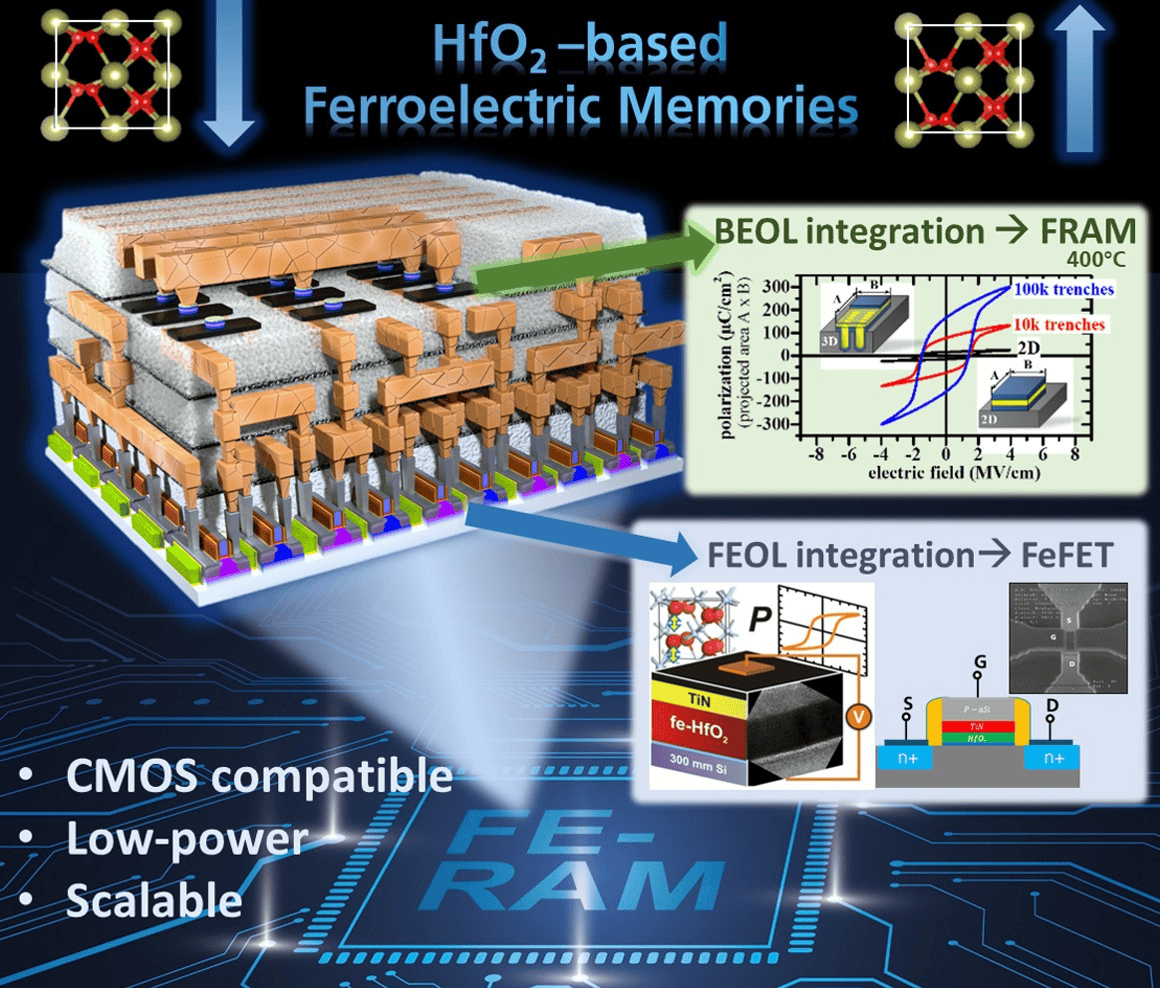

Looking ahead, the wafer loops lay the groundwork for broader collaborative development. Upcoming phases will integrate HfO₂-based ferroelectric stacks from Fraunhofer IPMS into CEA-Leti CMOS processes, followed by array-level evaluations of state-of-the-art memory technologies embedded in the upcoming GlobalFoundries’ 22nm FDX® Memory Advanced Demonstrator Multi Project Wafers shuttle prepared by CEA-Leti. The roadmap also includes studies on electrode process variations, long-term reliability, and back-end-of-line integration approaches.

In parallel, Fraunhofer IPMS recently completed a first chip tape-out using GlobalFoundries’ 22nm FDX® technology and initiated research on algorithm-based AI compute-in-memory accelerator architectures built on these ferroelectric technologies.

Together, these efforts advance the core mission of the FAMES Pilot Line: to provide a unified European platform for developing and validating emerging memory technologies—including OxRAM, MRAM, FeRAM, and FeFET. By enabling collaborative material development and standardized characterization, the initiative aims to strengthen Europe’s capacity to design and manufacture the low-power, next-generation chip architectures required for the future of computing.

Illustration von ferroelektrischen Bauelementen auf HfO₂-Basis, die skalierbare, CMOS-kompatible nichtflüchtige Speicher ermöglichen. Die Architektur unterstützt die Integration sowohl in Front-End- (FeFET) als auch in Back-End-Speicherstrukturen und eröffnet gleichzeitig Möglichkeiten für fortschrittliche ferroelektrische Funktionen wie multiferroische, pyroelektrische und abstimmbare HF-Bauelemente.

© Fraunhofer IPMS

👉Press Release