Mit dem Bereich Center Nanoelectronic Technologies CNT des Fraunhofer IPMS sowie dem Institutsteil ASSID des Fraunhofer-Instituts für Zuverlässigkeit und Mikrointegration IZM sind zwei bundesweit einzigartige Forschungseinrichtungen auf dem Gebiet der Mikroelektronik in Sachsen angesiedelt. Es sind heute die beiden einzigen deutschen Forschungszentren für angewandte Mikroelektronikforschung, die auf Basis von 300-mm-Wafer-IndustriestandardEquipment forschen. Im Kern des Konzeptes zur Gründung eines gemeinsamen Centers stand die Zusammenführung der wissenschaftlich-technischen Kompetenzen von IZM-ASSID und IPMS-CNT hinsichtlich der Forschung und Entwicklung (F&E) in 300-mm-Frontend-und -Backend-Prozessen. Damit wird zum einen Effizienzsteigerung sowie Vervollständigung der Wertschöpfungskette realisiert und eröffnet zugleich neue Forschungsfelder.

Material-Screening und Evaluierungsdienstleistungen

Eine wichtige Voraussetzungen für Kooperationen mit Industriepartnern ist der industriekompatible Reinraum des neuen Centers, in dem sich auf ca. 3 000 m² eine F&E-Technologieplattform mit einem Anlagenbeschaffungswert von mehr als 120 Mio. Euro befindet. Entscheidend ist, dass neben den Prozessanlagen auch die dazugehörige Logistik (wie Stocker und Sorter) sowie das gesamte Mess-und Analytikequipment auf dem 300-mmIndustriestandard basieren. Das IPMS-CNT betreibt dabei angewandte Forschung im Frontend der CMOS-Herstellung. Das Fraunhofer IZM-ASSID ergänzt diese Expertise mit innovativen Packaging-und Heterointegrations-Technologien.

Symbolische Waferübergabe zur feierlichen Eröffnung des „Center for Advanced CMOS & Heterointegration Saxony“ im Juni 2022 (Fotograf Christian Schneider-Bröcker)

Das neue Center bietet Halbleiter-Herstellern und -Zulieferern Screening und Evaluierungsdienstleistungen für Materialien, Prozesse, Chemikalien und Verbrauchsmaterialien vom Labor-bis zum Produktionsmaßstab an. Die Leistungen umfassen dabei Verbrauchsmaterial-Benchmarking, Prozessentwicklung, Ultra Large Scale Integration (ULSI), Pilotproduktion und Evaluation von Equipment. In produktionsähnlicher Umgebung mit Standard-Industrieausrüstung erfolgt eine unabhängige Auswertung und Versuchssteuerung mit ISO-9001-Zertifizierung. Dies beinhaltet einen direkten Austausch von Wafern mit Produktionslinien (Short Loops) und professionelles Kontaminationsmanagement. Es werden Pre-und Post-Processing einzelner Prozessschritte optimiert, um eine schnelle Skalierung vom Labormaßstab hin zur Einsatzfähigkeit in einer Hochvolumenfabrik zu ermöglichen. Das Center kann dabei auf mehr als 10 Jahre Erfahrung bei der Einführung neuer Materialien in die Fertigung zurückgreifen und bietet somit Kunden eine Einsparung von Ressourcen, Anlagen-Invests, Personal und Zeit (Time-to-Market).

Einblick in die Halbleiter-Forschung und –Fertigung

Einzelprozessentwicklung

Eine wichtige Kernaufgabe des Centers ist die Entwicklung, Optimierung und der Transfer von Prozess-und Integrationskonzepten mit Industriepartnern. Ein Beispiel hierfür ist die Entwicklung neuartiger Speichertechnologien u. a. für den langjährigen Industriepartner Globalfoundries. Die vom Fraunhofer IPMS im Reinraum und Laboren betriebene Forschung an innovativen Prozessen bildet die Grundlage für neue zuverlässige Speicherkonzepte, wie sie in eingebetteten Speicherblöcken sowie zukünftigen neuromorphen Rechenkonzepten zur Anwendung kommen.

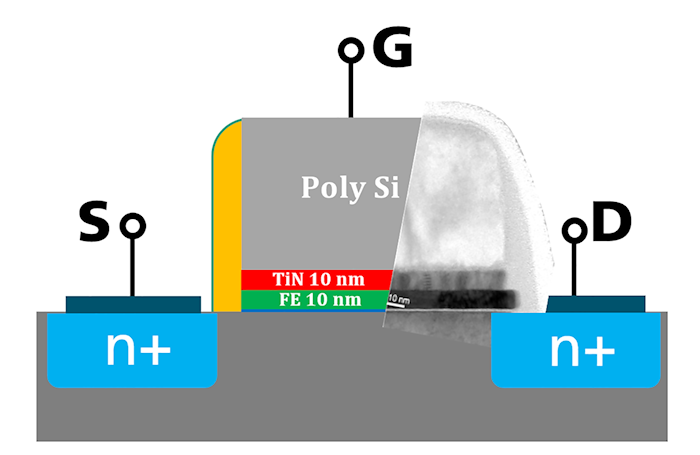

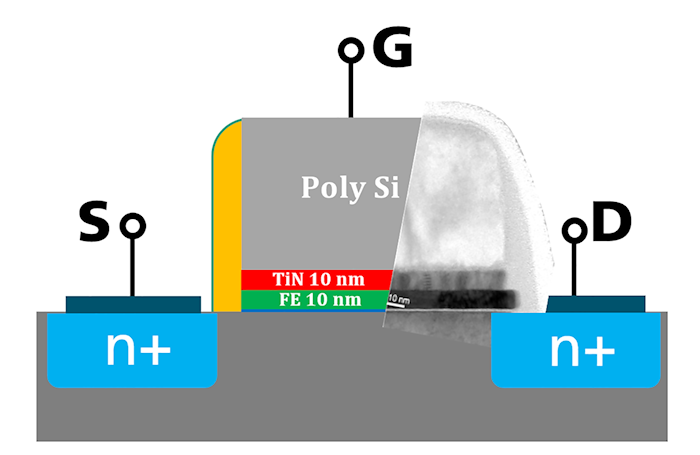

Das am IPMS erforschte ferroelektrische Hafniumoxid bietet viel Potenzial für den Einsatz in zukünftigen Chip-Generationen für einen breiten Anwendungsbereich. Durch die merkfähige Polarisationseigenschaft der ferroelektrischen Kristallstrukuren kann dieses Material für nichtflüchtige Datenspeicher eingesetzt werden. Solche Konzepte befinden sich bereits seit vielen Jahren in der Anwendung. Jedoch basieren die konventionellen ferroelektrischen Speicher oft auf bleihaltigen Materialien, wie Blei-Zirkonat-Titanat (PZT), die einerseits besondere Vorkehrungen bei der Bearbeitung im Reinraum erfordern und andererseits schlechter skalierbar sind. Dagegen ist Hafniumoxid bei neueren Transistorgenerationen ein etabliertes Gate-Dielektrikum, welches durch gezielte Dotierung durch z. B. Silizium mit ferroelektrischen Eigenschaften versehen werden kann. Beim Einbetten dieses ferroelektrischen Materials in Feldeffekttransistoren entstehen FeFET-Speichertransistoren (Abb. 1), die sich aufgrund der sehr dünnen ferroelektrischen Schicht sehr gut skalieren und auch mit niedrigen Spannungen schalten lassen.

Abbildung 1: FeFET-Speichertransistor der IPMS-Technologieplattform (Quelle aller Abbildungen: Fraunhofer IPMS).

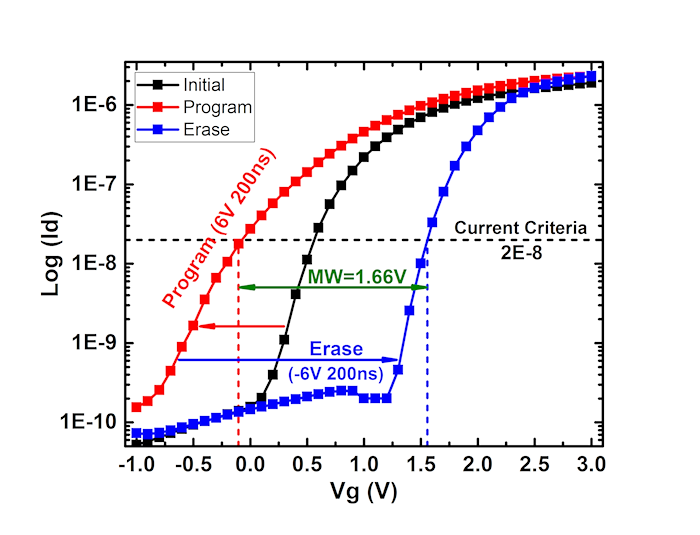

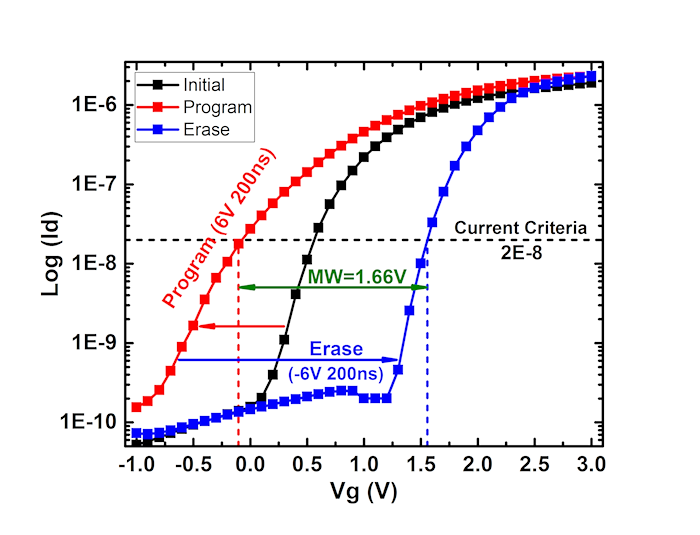

Durch Anlegen von elektrischen Feldern lässt sich die Polarisation der ferroelektrischen Dipole umschalten. Mit der Feldwirkung dieser Dipole kann der Arbeitspunkt der FeFETs verschoben und damit die gespeicherte Information zerstörungsfrei ausgelesen werden (Abb. 2).

Abbildung 2: Strom-Spannungs-Charakteristik eines FeFET-Speichertransistors für die beiden Speicherzustände programmiert (rot) und gelöscht (blau).

Neben der sehr hohen Schaltgeschwindigkeit und geringen Energieaufnahme liegt ein weiterer großer Vorteil in der einfachen Integrierbarkeit in bestehende Halbleiter-Technologien.

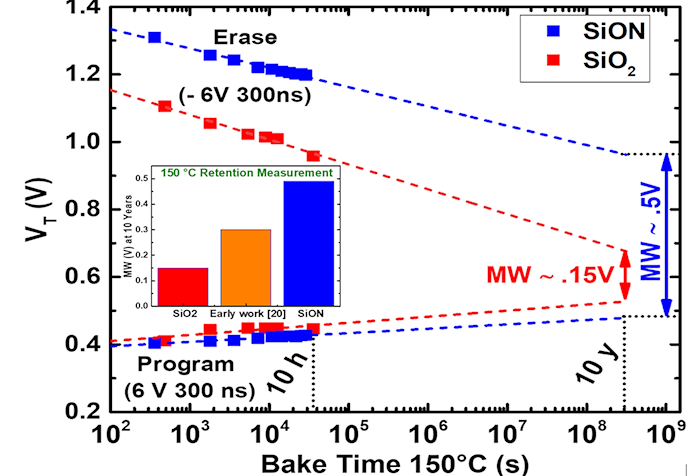

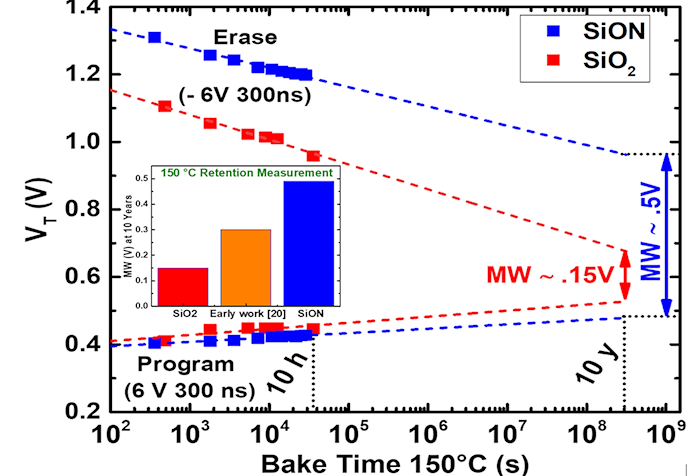

Im Rahmen eines Forschungsprojekts wurden am Fraunhofer IPMS für den Industriepartner Globalfoundries neue Ansätze für den ferroelektrischen Materialstapel in FeFET-Transistoren durch Prozessversuche erforscht. Mit Hilfe einer im Reinraum etablierten FeFET-Technologieplattform sowie Waferaustausch mit Globalfoundries wurden innovative Prozessvarianten für die Optimierung der Zuverlässigkeit und des Schaltverhaltens von ferroelektrischen Transistoren entwickelt und erprobt. Z. B. konnte mit einer auf Siliziumnitrid basierten Grenzfläche die Datenhaltung der Speicherzellen deutlich gesteigert werden (Abb. 3). Diese Prozessoptimierung konnte bei Globalfoundries etabliert und auf skalierten Speicherzellen im Megabit-Bereich erfolgreich demonstriert werden.

Abbildung 3: Vergleich der Datenhaltung für 2 Grenzflächenvarianten. Mit der Nitrid-Grenzfläche konnte in Versuchen eine deutliche Verbesserung der Datenhaltung erzielt werden.

Screening und Evaluierungsdienstleitungen

Das IPMS-CNT bietet neben der Einzelprozessentwicklung und Prozessoptimierung auch Screening und Evaluierungsdienstleistungen für Materialien, Prozesse, Chemikalien und Verbrauchsmaterialien an, die in Halbleiter-Fabriken benötigt und eingesetzt werden. So besteht zwischen dem CNT und BASF SE bereits seit 2014 ein langjähriger Kooperationsvertrag, welcher beabsichtigt gemeinsam innovative Lösungen für die Halbleiterindustrie zu entwickeln. Dabei werden neue Chemikalien für Halbleiter-Prozesse wie Plating und Bonding getestet sowie Prozessoptimierungen durchgeführt. BASF hat in diesem Zusammenhang eine entsprechende Prozess-Anlage eines renommierten Herstellers im CNT installiert. Diese moderne Plating-Prozessanlage zur galvanischen Abscheidung von Kupferschichten auf 300-mmWafermaßstab wird von den Forschenden des Fraunhofer-Centers betrieben.

Die verwendeten Technologien in dem Screening umfassen Dual-Damascene-Plating-Prozesse für sehr kleine Technologieknoten bis <20 nm sowie Packaging-Technologien zur Chipverdrahtung, bei welcher Leiterbahnmaterialien mittels RDL1) -, TSV2) -, Pillar-und Bump-Plating für Wafer-Level-Packaging-Anwendungen hergestellt werden.

Die Arbeiten des Fraunhofer-Centers umfassen innerhalb des Kooperationsvertrages zum einen den Bereich Forschung und Entwicklung. Dabei werden im Bereich des Elektroplatings neuentwickelte Produkte getestet und Ramp-ups auf Industriemaßstab durchgeführt. Dies umfasst das Screening von Chemikalien, Elektrolyten und Badadditiven, um hochreine Metallschichten abzuscheiden, die bei der Chipfertigung später in Verdrahtungsstrukturen eingesetzt werden sollen. Das Fraunhofer-Center prüft mittels der Anlage, ob z. B. die Abscheidung mit neuen sich in der Entwicklung befindlichen Elektrolyten partikelarm erfolgt und auf dem Wafer eine homogene Schicht erzeugt. Ebenso stehen Eigenschaftsuntersuchungen der abgeschiedenen Schichten, wie z. B. Korngröße und -orientierung im Fokus.

Der zweite Arbeitsbereich umfasst die Demonstration und Testversuche. Mithilfe der Anlage werden dabei neueste Technologien und innovative Chemikalien auf Testwafern bzw. Short-Loop-Wafern getestet und Prozessdaten maßgeschneidert für Kunden erzeugt. Darüber hinaus werden Parameteroptimierungen an Fertigungsprozessen durchgeführt, um diese weiterzuentwickeln und an neue Chipdesigns anzupassen. Die in den Tests zu erreichenden Zielparameterwerte für die Metallisierung für Verdrahtungsstrukturen umfassen das gute Strukturfüllen ohne Hohlräume sowie homogene Struktur-und Waferoberflächen. Da Fraunhofer die gleiche Anlagentechnik nutzt, wie sie auch bei den Kunden zum Einsatz kommt, ermöglicht dies eine signifikante Kosten-und Zeiteinsparung für den Chemiehersteller. Mit Abschluss der Pilottests am Fraunhofer-Center können Kunden somit die einsatzbereiten Prozesse zur Herstellung fortschrittlicher elektronischer Materialien unmittelbar nutzen. Die Weiterentwicklung von Materialen und Prozessen ermöglicht dabei den ständig steigenden Anforderungen an Mikrochips hinsichtlich Funktionalität, Schnelligkeit und Energieeffizienz gerecht zu werden.

Wafer-Charakterisierung im Reinraum und Labor-Bereich

Eine wichtige Rolle spielt die physikalische und elektrische Charakterisierung von Wafern im Reinraum und in den spezialisierten Analyse-Laboren. Um die Prozesse und Bauelemente der Nanotechnologie-Forschung hinsichtlich ihrer Anwendungseigenschaften und Zuverlässigkeit bewerten zu können, existiert am Fraunhofer-Center in Dresden ein breites Portfolio an hochempfindlicher elektrischer und physikalischer Messtechnik.

Elektrische Messtechnik am Fraunhofer Center (li. automatischer Waferprober, mi. halbautom. Waferprober, re. Halbleiter-Parameter-Analyzer)

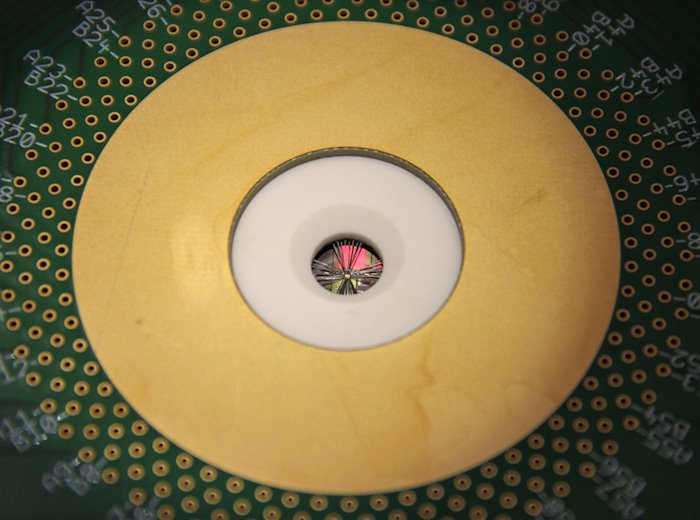

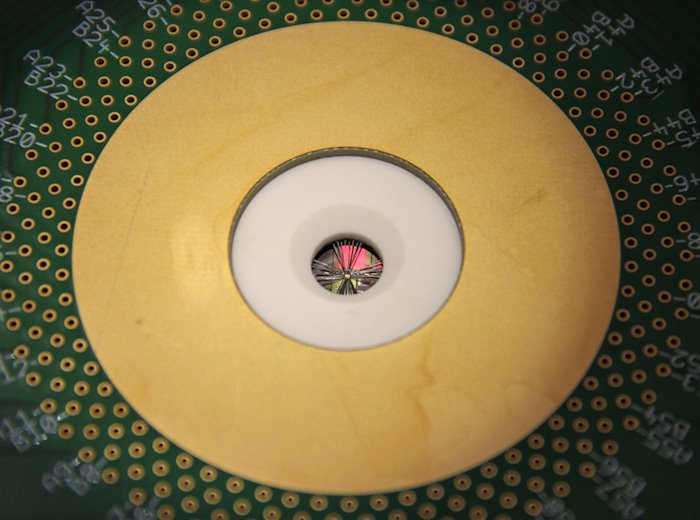

Dabei können bereits sog. Inline-Messungen während der Bearbeitung von Wafern im Reinraum zerstörungsfrei erste Einblicke in Funktionalität und elektrische Parameter der hergestellten Strukturen liefern. Somit sind schnelle Reaktionszeiten bzgl. Prozessanpassungen und Erkenntnisse zu den einzelnen Zwischenschritten möglich. Nach Fertigstellung und Ausschleusung der Wafer können diese mit tiefergehenden Analysemethoden unter Verwendung hochspezialisierter elektrischer und physikalischer Messtechnik analysiert werden. So werden die hergestellten Wafer dann im elektrischen Testlabor komplett oder als einzelnes Probenstück in Waferprobern geladen und die darauf befindlichen Bauelemente mittels mikrometerfeiner Probernadeln elektrisch kontaktiert.

Abbildung 4: Eine mit Probernadeln kontaktierte Teststruktur.

Über die angeschlossene Messtechnik ist es dann z. B. möglich, Kennlinienfelder von integrierten Transistoren, das Frequenzverhalten von Kondensatoren und Hochfrequenzstrukturen, das Schaltverhalten von Speicherzellen oder Leckströme von Dielektrika bis in den Femtoampere( fA)-Bereich zu charakterisieren, um nur einige zu nennen.

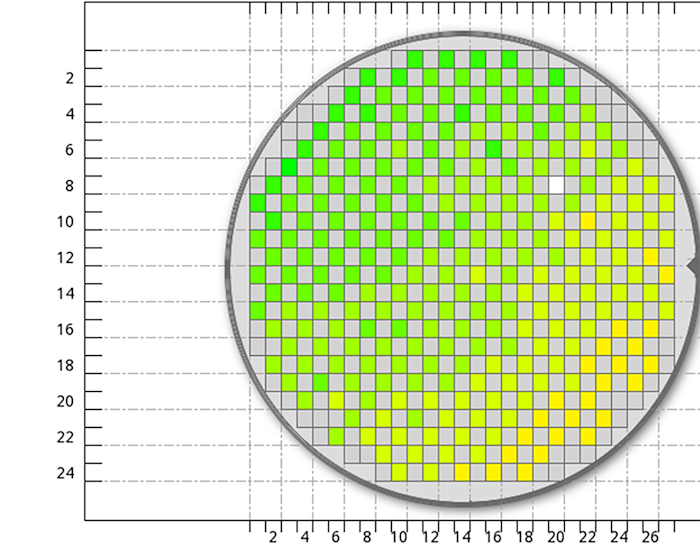

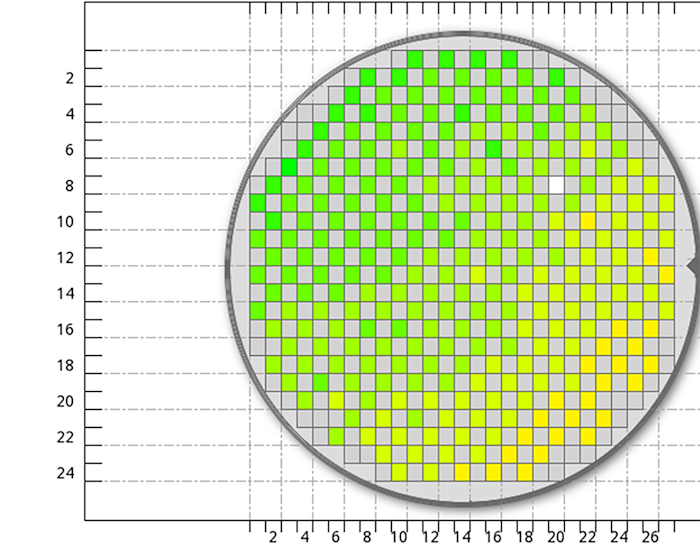

Eine wichtige Rolle kommt auch dem hohen Automatisierungsgrad der Messprozeduren zu, der es ermöglicht, mittels statistischer Messungen die elektrischen Eigenschaften über ganze Wafer zu bestimmen, um so Schlussfolgerungen über die Gleichförmigkeit der Waferprozesse im Reinraum ziehen zu können (Abb. 5).

Abbildung 5: Eine statistische Messung mit Schachbrett-Wafermap und Wafersignatur.

Diese konsequente Automatisierung der elektrischen Messtechnik, verbunden mit dem weiten Temperaturbereich der Waferprober von – 55 bis 300 °C ermöglicht auch komplexe, langwierige Messungen bei verschiedenen Testtemperaturen ohne manuelle Eingriffe und somit wissenschaftliche Forschung zu physikalischen Vorgängen in Materialien sowie auch die Betrachtung von Zuverlässigkeit in realen Anwendungsszenarien wie sie in der Industrie und Automobiltechnik vorkommen.

Wie bereits erwähnt, ist ein wichtiger Schwerpunkt im elektrischen Testlabor am Fraunhofer-Center die Charakterisierung von nichtflüchtigen Datenspeichern. Hier können einzelne Speicherelemente oder auch komplexe Speicherblöcke im GigabitMaßstab hinsichtlich Leistungsfähigkeit, Datenhaltung und weiterer Zuverlässigkeitsparameter statistisch untersucht werden.

Für die Mixed-Signal-Foundry XFAB werden umfangreiche Tests und Messungen durchgeführt, um deren Chips zu verbessern. Dabei werden in einem gemeinsamen Forschungsprojekt Speicher der nvSRAM-Technologie analysiert. Ein nvSRAM verknüpft die Vorteile eines sehr schnellen aber flüchtigen SRAM-Speichers mit den Eigenschaften eines nichtflüchtigen Speichers durch Integration entsprechender Speicherzellen in die SRAM-Schaltungen. So kann bei einem Stromausfall im System der Inhalt des SRAM innerhalb weniger Millisekunden abgesichert und somit ein Datenverlust verhindert werden. Am Fraunhofer-Center werden größere nvSRAM-Speicherblöcke von X-FAB mittels schneller Mixed-Signal-Testsysteme (24 analoge und 96 digitale Kanäle) hinsichtlich ihrer Schalteigenschaften, Fehlerrate und Zuverlässigkeit unter Automotive-Bedingungen untersucht. Mit den Messergebnissen können gezielt Speichertechnologie und Schaltungsdesign optimiert werden.

Kooperationen des Centers

Die Umsetzung gemeinsamer Forschungsprojekte und Kooperationen mit Industrieunternehmen ist eine Kernaufgabe von Fraunhofer. So hat der Bereich CNT des Fraunhofer IPMS bereits mit über 100 Kunden Projekte umgesetzt. Rund ein Viertel der Industrieerträge stammen dabei aus Sachsen, die Hälfte aus Deutschland (ohne Sachsen). Zu den größten Kunden zählen Globalfoundries, Infineon und X-FAB. Neben Aufträgen der großen sächsischen Halbleiter-Fertiger bestehen zahlreiche Kooperationen mit kleineren sächsischen Unternehmen, die z. B. aufgrund von geringen Stückzahlen oder spezifischer Materialanforderungen keinen Zugang zu Halbleiter-Foundries besitzen. Das CNT ist auch für die Halbleiter-Zuliefererindustrie ein bedeutender Partner. So konnte eine neuartige umweltschonende Wafer-Reinigungstechnologie eines Leipziger Start-ups (Intelligent Fluids) am CNT erstmals unter Industriebedingungen getestet werden. Auf Grundlage der Projektergebnisse erfolgt nun der Einsatz direkt bei Halbleiter-Herstellern weltweit. Die langjährige Kooperation mit BASF zum Test und der Weiterentwicklung von Chemikalien für die Chipherstellung ist ein weiteres Beispiel für eine erfolgreiche Kooperation.

Auch im Rahmen des Leistungszentrums „Funktionsintegration für die Mikro-/Nanoelektronik“ sowie der Forschungsfabrik Mikroelektronik Deutschland (FMD) wird das Center for Advanced CMOS & Heterointegration Saxony als Integrationsplattform in kundenspezifischen Projekten genutzt. So sind das Fraunhofer IPMS sowie das Fraunhofer IZM-ASSID Partner im Projekt „300-mm-WaferHub“des Leistungszentrum Funktionsintegration für die Mikro-/Nanoelektronik. Durch die im Projekt realisierte engmaschige Verknüpfung von Prozesstechnologieentwicklung, applikationsspezifischen Anwendungen und Analytik der beiden Fraunhofer-Institute wurden Synergien gewonnen, die es im Leistungszentrum ermöglichen anspruchsvolle strukturierte Testvehikel und Testsubstrate zu schaffen und anzubieten. Diese können Kunden und Partnern sowohl direkt zur Evaluation zur Verfügung gestellt als auch in weiteren Industrieprojekten eingesetzt werden. Die Technologien kommen dabei sowohl vom Front-End-of-Line (FEoL), in welchem High-k und epitaktische Si(Ge)-Schichten angeboten werden, als auch vom Back-End-of-Line (BEoL) und Packaging, in welchen die Metallisierung vor allem mittels Kupfer und dessen Einbettung eine Rolle spielt.

Weitere Kooperationen bestehen mit sächsischen Universitäten, besonders der TU Dresden, sowie zur außeruniversitären Forschung (z. B. HZDR, IFW). Beispielhaft dafür ist die Kooperation mit dem Max-Plack-Institut für Strukturphysik in Halle, gemeinsam wird gerade eine neue vielversprechende Forschungskooperation im Bereich magnetischer Speicher realisiert.

Auf europäischer Ebene besteht eine enge Vernetzung zwischen dem Fraunhofer Verbund Mikroelektronik, dem CEA-LETI in Grenoble (Frankreich) sowie dem IMEC in Leuven (Belgien). Die 3 europaweit führenden Research-and-Technology-Organisationen (RTOs) im Bereich Mikroelektronik koordinieren ihre F&E-Aktivitäten zunehmend. So wurden für das aktuelle europäische Forschungsrahmenprogramm (HorizonEurope) gemeinsame Forschungsschwerpunkte nach dem Ansatz der Smart Specialization abgestimmt und z. B. durch einen gemeinsamen Antrag zur Schaffung einer europäischen Testing and Experimentation Facility (TEF) for Edge AI umgesetzt.

Das CNT spielt in dieser europäischen Kooperation gemeinsam mit dem IZM-ASSID für Deutschland im Bereich der industrienahen 300-mmForschung eine Schlüsselrolle. Ohne diese beiden Forschungsstandorte könnte Deutschland auf diesem Gebiet im europäischen Halbleiter-Forschungs-Dreieck Grenoble–Leuven–Dresden keine adäquate Partnerrolle einnehmen.

International ist auch das Fraunhofer IZM-ASSID eng verflochten mit Arbeitsgruppen im Bereich Wafer-Level-Integration, u. a. mit Heterogeneous Integration Roadmap.

Blick in den Reinraum des neuen Centers auf den 300 mm Industriestandard Anlagen

Fazit und Ausblick

Die Chips der Zukunft sollen 3-dimensional, energie-und chemikaliensparend, umweltgerecht und preiswert sein. Durch die zukünftig noch enger verzahnte gemeinsame Arbeit der Fraunhofer Kollegen im neuen Center for Advanced CMOS & Heterointegration Saxony bestehen beste Voraussetzung, dass in Zukunftstechnologien wichtige Impulse und Forschungsergebnisse aus Sachsen kommen werden.

So forschen die Wissenschaftler des Centers im Bereich Quantencomputing gemeinsam daran, dass die Quantenherstellung in Zukunft mittels herkömmlicher Halbleiterprozesse (CMOS-kompatibel) erfolgen kann und damit kostengünstiger und zugleich skalierbarer wird. Das Center stellt dabei eine Brückenfunktion zwischen der universitären Grundlagenforschung und der industriellen Anwendung dar.

Im Bereich Neuromorphic Computing arbeiten die Forschenden an neuen Speicherbauelementen und Beschleunigern an In-Memory-Computing-Lösungen für besonders energieeffiziente KI-basierte Sensorlösungen. Die Datenvorverarbeitung direkt am Sensor ist dabei wesentlich energiesparender, schneller und auch kostengünstiger als aktuelle cloudbasierte Lösungen.

Serviceleistungen

Das Center bietet neben direkter Auftragsforschung für Unternehmen und der F&E-Zusammenarbeit in öffentlich geförderten Projekten zahlreiche Dienstleistungen an, wie z. B.:

•Nanopatterning mittels E-Beam-Lithografie für verschiedenste Substrate (z. B. Si-Glas) und Größen

•Prozessierung von Wafern (bis 300 mm) mit kundenspezifischem Schichtaufbau

•Test-Wafer-Evaluation

•Untersuchungen zu einzelnen Prozessschritten wie chemisch-mechanisches Polieren (CMP), Atomlagenabscheidung (ALD), reaktives Ionentiefenätzen (DRIE) und Kupferbeschichtung (Cu-Plating)

•Wafer-Reinigung

•Screening und Optimierung neuer Chemikalien und Prozesse bis zur 2x-nm-Node

•Qualifikation von Anlagen und Komponenten für die Hochvolumen-Halbleiter-Fertigung unter Standard-Industriebedingungen

Weitere Informationen unter: https://www.ipms.fraunhofer.de/de/Services/300mm-semiconductor-processes.html