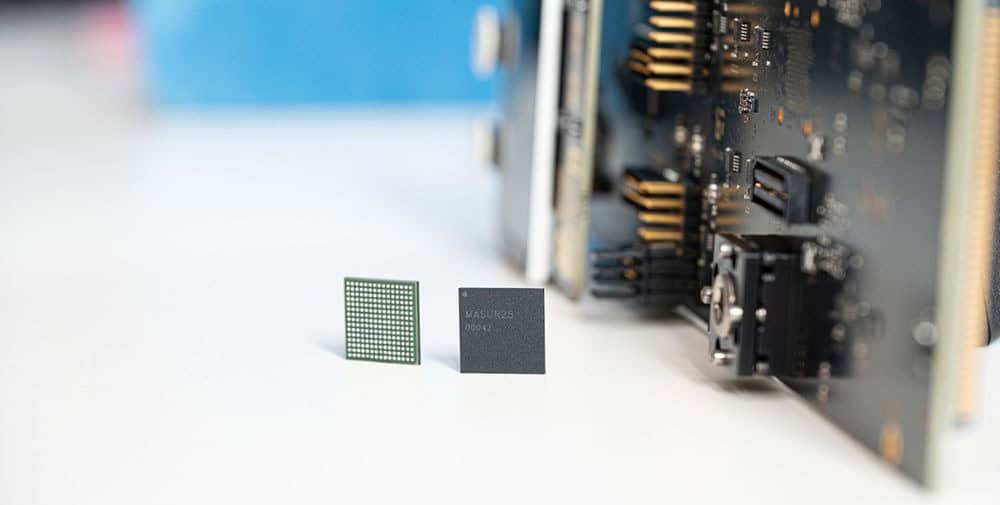

Wenn IC-Designs in fortschrittlichere Nodes bei 5 nm und darunter vordringen, werden sie zunehmend anfällig für Fertigungsschwankungen, die Defekte verursachen und die Ausbeute verlangsamen können. Bei diesen Geometrien können herkömmliche Methoden der Fehleranalyse (FA) wochen- oder monatelange Laboruntersuchungen erfordern. Das neue Tessent-Hi-Res-Chain-Tool von Siemens löst dieses Problem, indem es schnell eine Isolierung auf Transistorebene für Scan-Chain-Defekte liefert. Bei fortgeschrittenen Prozessknoten, bei denen die Steigerung der Ausbeute stark von der Kettendiagnose abhängt, kann die neue Software die Diagnoseauflösung um mehr als das 1,5-fache erhöhen und so den Bedarf an kostspieligen, umfangreichen Fehleranalysezyklen reduzieren.

„Tessent Hi-Res Chain stellt einen großen Schritt nach vorn dar, wenn es darum geht, ertragsbegrenzende Faktoren in fortschrittlichen IC-Designs schnell zu identifizieren und zu beseitigen“, sagte Ankur Gupta, Vice President und General Manager des Geschäftsbereichs Digital Design Creation Platform, Siemens Digital Industries Software. „Indem wir eine noch nie dagewesene Genauigkeit und Auflösung bei der Defektisolierung bieten, ermöglichen wir unseren Kunden, ihre Ausbeute zu beschleunigen und die Markteinführungszeit für innovative Halbleiterprodukte zu verkürzen.“

Durch die Korrelation von Designinformationen und Fehlerdaten aus Fertigungstests mit Mustern aus der automatischen Testmustergenerierung (ATPG) von Tessent verwandelt Tessent Hi-Res Chain fehlerhafte Testzyklen in verwertbare Erkenntnisse. Die Lösung nutzt Layout- und Cell-Aware-Technologie, um den wahrscheinlichsten Fehlermechanismus, die logische und physikalische Position eines Fehlers zu ermitteln.

Tessent Hi-Res Chain baut auf den marktführenden Kettendiagnose-Fähigkeiten von Siemens auf und bietet eine präzise Fehlerisolierung, selbst bei punktuellen Defekten tief in den Netzwerken der Design-Steuersignale.

Die neue Lösung behält die branchenführende Genauigkeitsrate von Tessent bei, wobei über 80 Prozent der generierten Berichte durch FA-Prozesse mit Tessent-Technologie bestätigt werden. Dieses hohe Maß an Zuverlässigkeit hat Tessent zur bevorzugten Lösung für das Yield Ramping über mehrere Technologieknoten hinweg gemacht.

Tessent Hi-Res Chain ist Teil der umfassenden Tessent-Produktfamilie von Siemens, die branchenführende Lösungen für IC-Test, Funktionsüberwachung und Silizium-Lebenszyklus-Management bietet. Diese Tools arbeiten zusammen, um die höchste Testabdeckung zu erreichen, die Ausbeute zu beschleunigen und die Qualität und Zuverlässigkeit während des gesamten Lebenszyklus des Siliziums zu verbessern.

Weitere Informationen über Tessent Hi-Res Chain und die gesamte Palette der IC-Design- und Testlösungen von Siemens finden Sie unter www.siemens.com/tessent.

Siemens Digital Industries Software unterstützt Unternehmen jeder Größe bei der digitalen Transformation mit Software, Hardware und Services der Siemens Xcelerator Business Platform. Die Software von Siemens und der umfassende digitale Zwilling ermöglichen es Unternehmen, ihre Entwurfs-, Konstruktions- und Fertigungsprozesse zu optimieren, um die Ideen von heute in nachhaltige Produkte der Zukunft zu verwandeln. Vom Chip bis zum Gesamtsystem, vom Produkt bis zum Prozess, über alle Branchen hinweg. Siemens Digital Industries Software-Beschleunigung der Transformation.

– – – – –

Weiterführende Links

👉 www.siemens.com

Foto: Siemens