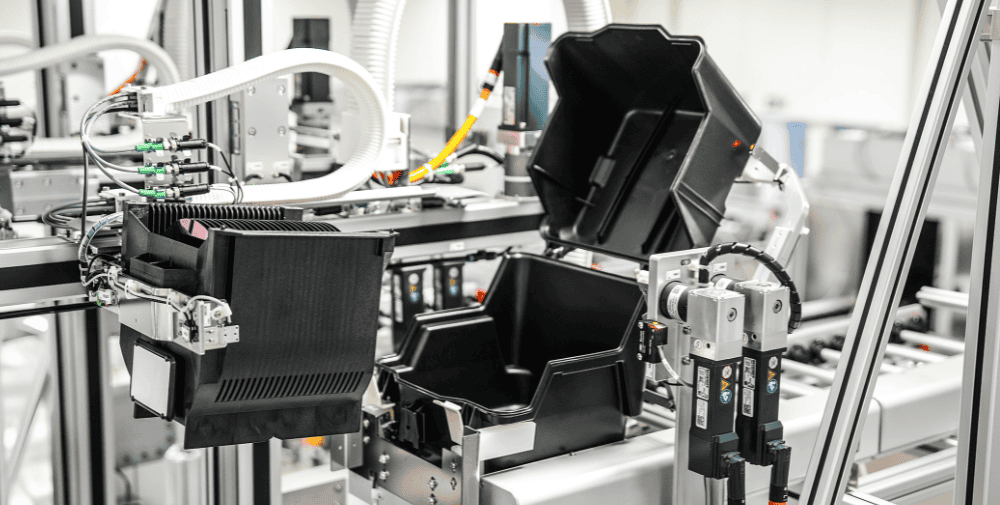

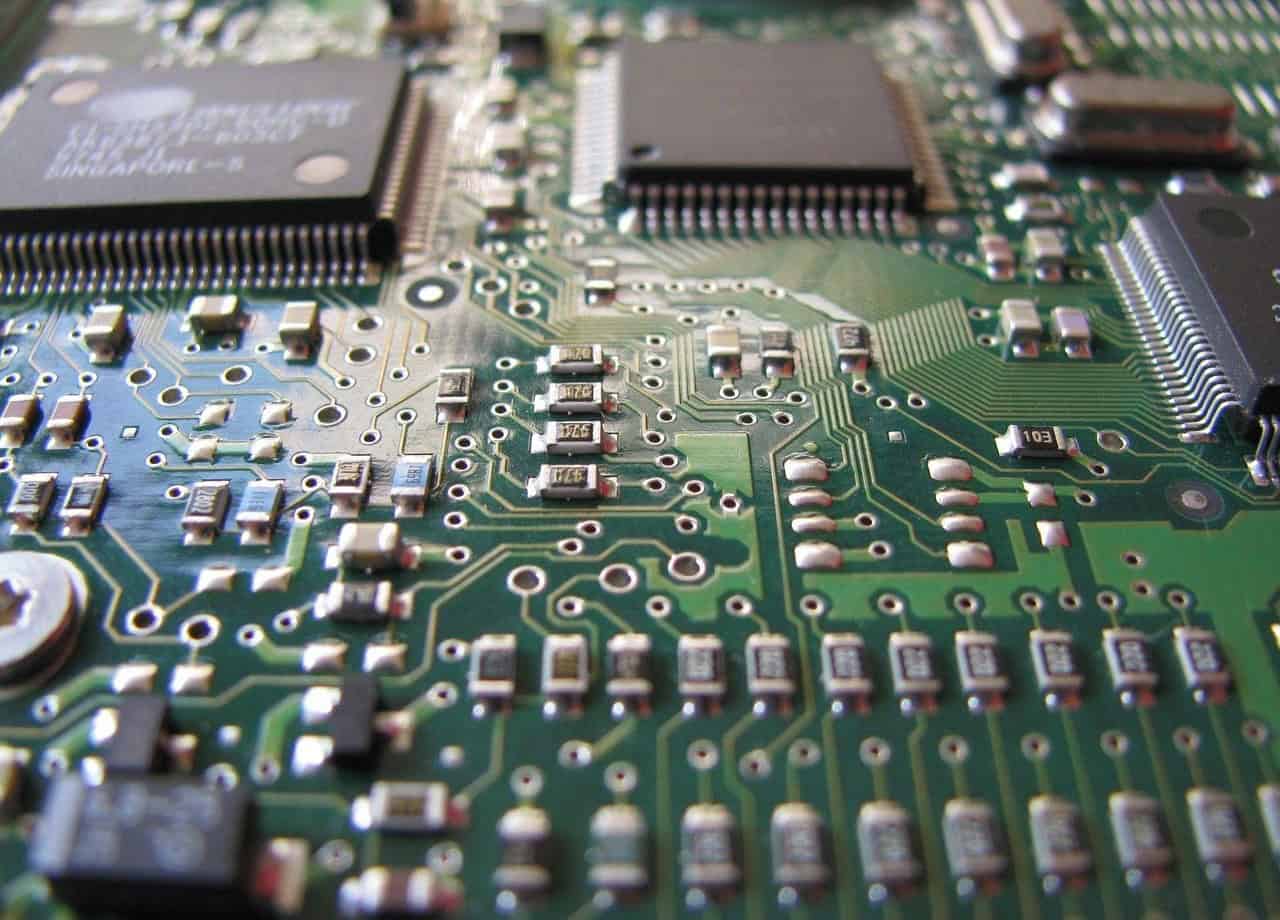

Siemens hat heute in enger Zusammenarbeit mit NVIDIA bekannt gegeben, dass sein hardwaregestütztes Verifikations- und Validierungssystem Veloce™ proFPGA CS Designern und Systemarchitekten die Möglichkeit bietet, noch stärker optimierte Designs zu erstellen. Dazu werden Billionen von Verifikationszyklen durchgeführt und erfasst, noch bevor der erste Siliziumchip verfügbar ist.

Im Rahmen ihrer langjährigen strategischen Partnerschaft haben NVIDIA und Siemens eine Aufgabe gemeistert, die bislang als unmöglich galt: Sie erfassten in nur wenigen Tagen mehrere zehn Billionen von Zyklen, indem sie die skalierbare und leistungsoptimierte Hardwarearchitektur Veloce proFPGA CS von Siemens mit der leistungsoptimierten Chiparchitektur von NVIDIA kombinierten.

„NVIDIA und Siemens arbeiten in vielen Bereichen zusammen, zuletzt bei der Weiterentwicklung hardwaregestützter Verifizierungsmethoden im Allgemeinen und beim Prototyping auf FPGA-Basis im Besonderen. Ziel ist es, den Anforderungen an Verifizierung und Validierung gerecht zu werden, die hochkomplexe KI-/ML-SoCs mit sich bringen“, erklärt Jean-Marie Brunet, Senior Vice President und General Manager, Hardware Assisted Verification, Siemens Digital Industries Software. „Veloce proFPGA CS behandelt diese Herausforderungen, indem es eine hochflexible und skalierbare Hardwarearchitektur mit einem fortschrittlichen, benutzerfreundlichen Software-Workflow für die Implementierung und das Debugging kombiniert. So erhalten Kunden stets die optimale Lösung sowohl für die Validierung von Single-FPGA-IP als auch für Chiplet-Designs mit mehreren Milliarden Gates.“

„Da KI- und Rechnerarchitekturen immer komplexer werden, benötigen Halbleiterteams leistungsstarke Verifizierungslösungen, um umfangreiche Arbeitslasten zu validieren und die Markteinführungszeit zu verkürzen“, erklärt Narendra Konda, Vice President of Hardware Engineering bei NVIDIA. „Durch die Integration der leistungsoptimierten Chiparchitekturen von NVIDIA mit dem Veloce proFPGA CS von Siemens können Entwickler innerhalb weniger Tage Billionen von Zyklen erfassen und damit die erforderliche Skalierbarkeit erreichen, um die Zuverlässigkeit der nächsten Generation von KI zu gewährleisten.“

Prototypensysteme auf Basis von Field Programmable Gate Arrays (FPGA) sind schnell und ermöglichen es Benutzern, Verifizierungsaufgaben vor der Hardwarefertigung in einem Bruchteil der Zeit durchzuführen, die für die Ausführung derselben Aufgaben in der Simulation oder selbst in der Emulation erforderlich wäre. Die heutigen KI/ML-Designs stellen jedoch noch höhere Anforderungen, was zum Teil an der Chip-Komplexität und zum Teil an der Software-Komplexität liegt.

Um diese Branchenanforderungen zu erfüllen, die Markteinführungszeit einzuhalten und den Zuverlässigkeitsanforderungen gerecht zu werden, ist es heute entscheidend, Billionen von Designzyklen in kurzer Zeit abarbeiten zu können. Herkömmliche Verifizierungstools wie Simulation und Emulation erlauben keine Skalierung über den Millionenbereich hinaus oder können innerhalb eines angemessenen, praktikablen Zeitrahmens bestenfalls einige Milliarden Zyklen ausführen.

Um mehr darüber erfahren, wie Siemens die Halbleiter- und Elektronikindustrie dabei unterstützt, die weltweit fortschrittlichsten SoCs und Systeme auf den Markt zu bringen, besuchen Sie https://www.siemens.com/en-us/products/ic/hav/veloce-cs/profpga-cs/

_ _ _ _

Weiterführende Links

👉 Siemens