Die Zusammenarbeit konzentriert sich auf die Herstellung und elektrische Charakterisierung von ferroelektrischen Kondensatorstapeln aus Hafnium-Zirkoniumoxid (HZO). Unter Nutzung der kombinierten 300-mm-CMOS-Reinraumkapazitäten beider Institute wurden die Wafer in kurzen Prozessschleifen ausgetauscht, um eine gemeinsame Bewertung von Materialien, Elektrodenkonfigurationen und Bauelementverhalten zu ermöglichen. Bei der erfolgreichen Bearbeitung an zwei Standorten wurden auch die in der Pilotlinie implementierten Protokolle für den Waferaustausch und die Kontaminationskontrolle validiert und gezeigt, dass auch komplexe Materialstapel in verschiedenen Reinräumen auf allen Wafern zuverlässig verarbeitet werden können.

From Lab to Fab – schneller zu Anwendungen auf Systemebene

»Der erfolgreiche Waferaustausch ist ein wichtiger Schritt hin zu einer gemeinsamen europäischen Materialprüfplattform für ferroelektrische Speicher«, sagt Dr. Wenke Weinreich, Bereichsleiterin des Center Nanoelectronic Technologies des Fraunhofer IPMS und Mitglied des elfköpfigen FAMES-Konsortiums. »Durch die Kombination unserer Prozess-Expertise mit den CMOS-Integrationsfähigkeiten von CEA-Leti bietet die Pilotlinie eine leistungsstarke Umgebung für die Bewertung neuer ferroelektrischer Bauelemente und beschleunigt deren Weg zu Anwendungen auf Systemebene.«

Nahtloser Wafer-Austausch zwischen den FAMES-Standorten

»Dieser erste Austausch zwischen CEA-Leti und dem Fraunhofer IPMS zeigt, dass gemeinsame Prozessabläufe, Testvehikel und Charakterisierungsumgebungen nahtlos zwischen den FAMES-Standorten funktionieren können«, erklärt Projektkoordinator Dominique Noguet. »Die Einrichtung zuverlässiger Wafer-Loops zwischen führenden Forschungsinstituten ist für die Beschleunigung der Entwicklung ferroelektrischer Speicher unerlässlich.«

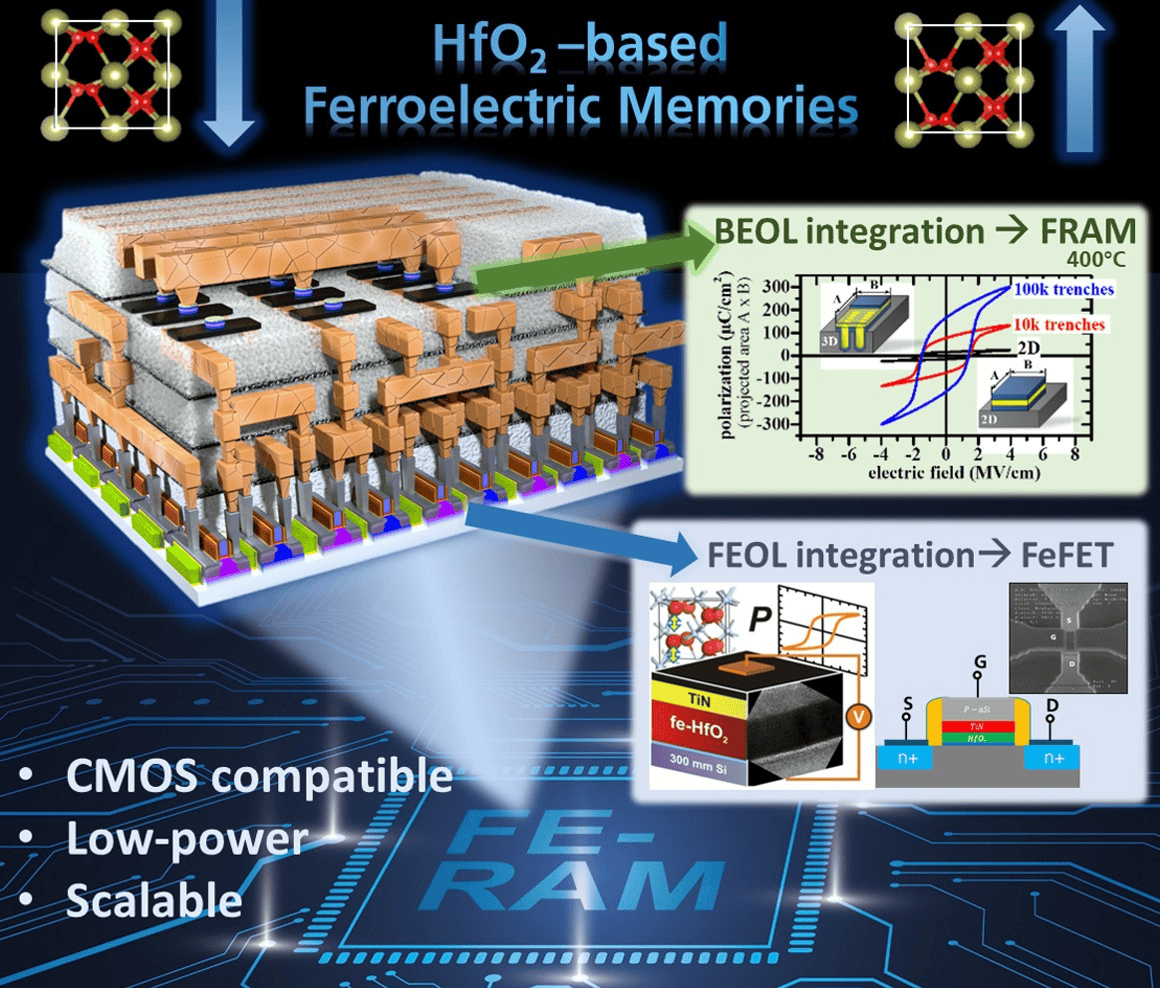

Mit Blick auf die Zukunft legen die Wafer-Loops den Grundstein für eine breitere Zusammenarbeit in der Entwicklung. In den nächsten Phasen werden HfO₂-basierte ferroelektrische Stapel von Fraunhofer IPMS in CEA-Leti-CMOS-Prozesse integriert, gefolgt von Bewertungen auf Array-Ebene von neuen Speichertechnologien. Die Roadmap umfasst auch Studien zu Elektrodenprozessvariationen, Langzeitzuverlässigkeit und Back-End-of-Line-Integrationsansätzen.

Parallel dazu hat das Fraunhofer IPMS kürzlich einen ersten Chip-Tape-out mit der 22-nm-FDX®-Technologie von GlobalFoundries abgeschlossen und mit der Forschung an algorithmischen KI-Compute-in-Memory-Beschleunigerarchitekturen begonnen, die auf diesen ferroelektrischen Technologien aufbauen.

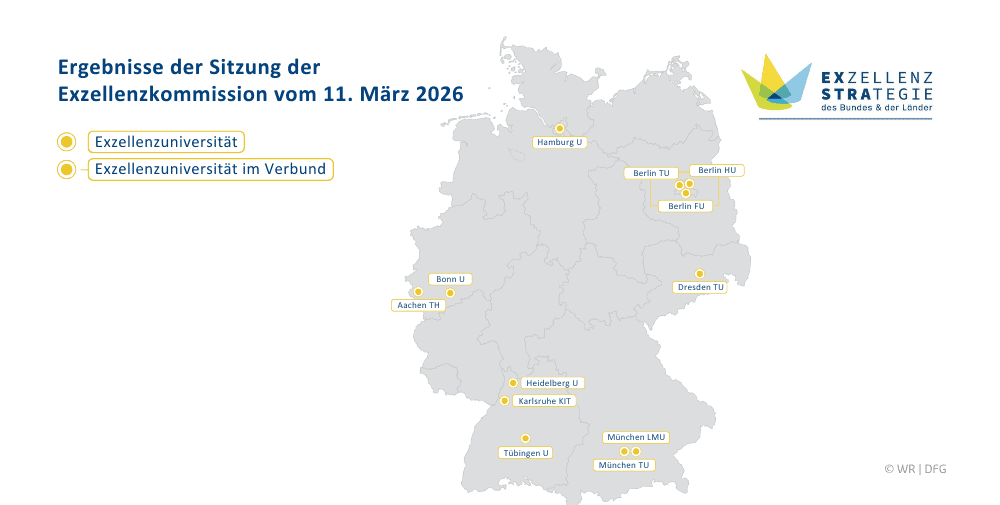

Zusammen tragen diese Bemühungen zur Kernaufgabe der FAMES-Pilotlinie bei: der Bereitstellung einer einheitlichen europäischen Plattform für die Entwicklung und Validierung neuer Speichertechnologien – darunter OxRAM, MRAM, FeRAM und FeFET. Durch die Förderung der gemeinsamen Materialentwicklung und standardisierten Charakterisierung soll die FAMES-Pilotlinie Europas Kapazitäten zur Entwicklung und Herstellung der für die Zukunft der Datenverarbeitung erforderlichen energiesparenden Chiparchitekturen der nächsten Generation stärken.

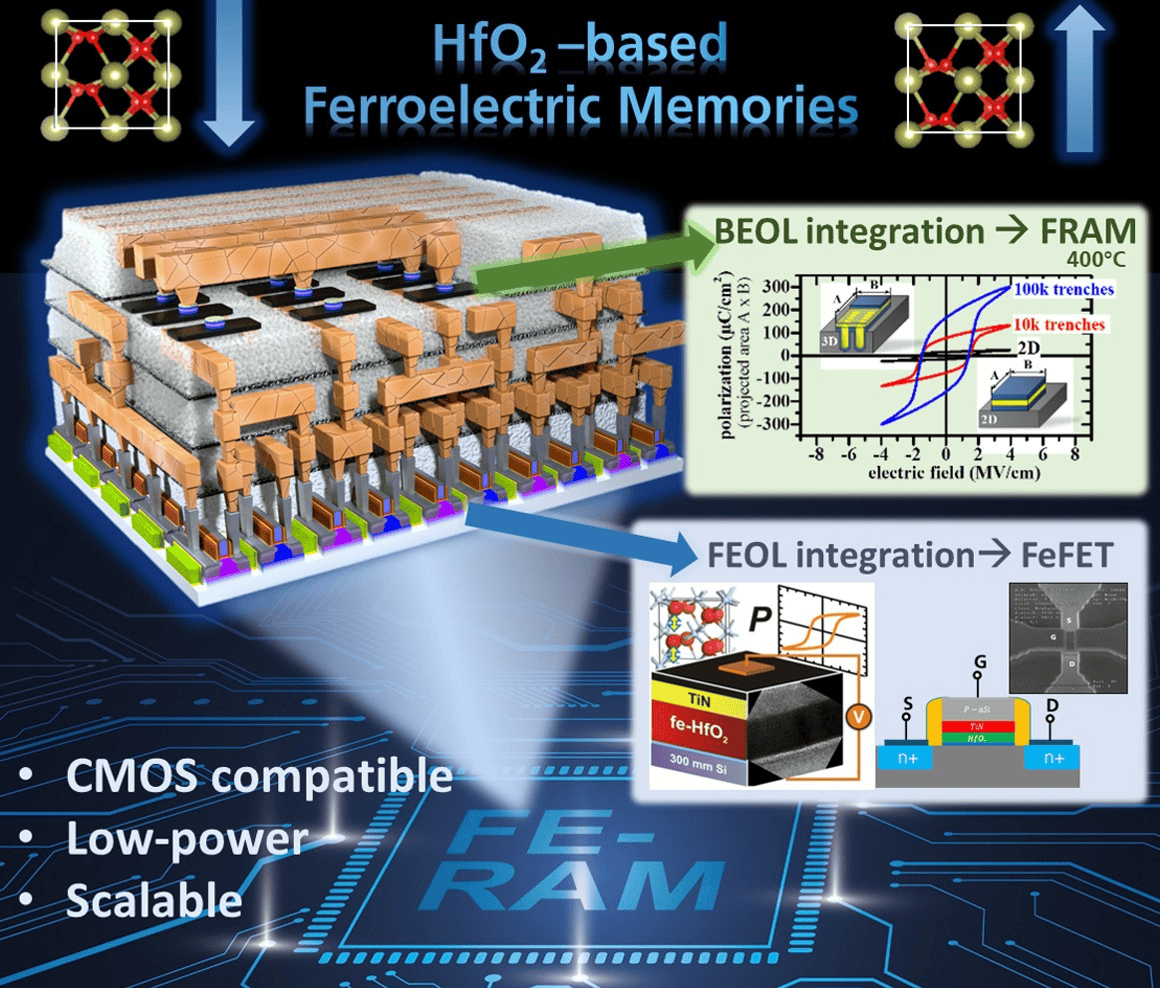

Illustration von ferroelektrischen Bauelementen auf HfO₂-Basis, die skalierbare, CMOS-kompatible nichtflüchtige Speicher ermöglichen. Die Architektur unterstützt die Integration sowohl in Front-End- (FeFET) als auch in Back-End-Speicherstrukturen und eröffnet gleichzeitig Möglichkeiten für fortschrittliche ferroelektrische Funktionen wie multiferroische, pyroelektrische und abstimmbare HF-Bauelemente.

© Fraunhofer IPMS

👉 Zur Pressemitteilung