Unternehmensart

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration – IZM ASSID

Zielmärkte

Branchen

Portfolio

Zertifikate

Kontakt

01468 Moritzburg

Ansprechpartner

Über das Mitglied

3D-Assembly and Interconnection Technologies

- Evaluation of die-to-wafer (D2W) and wafer-to-wafer (W2W) bonding for 3D stack formation

- 3D IC assembly with high-density interconnects (> 1000 I/O) and ultra-fine pitch (< 50 μm)

- 3D IC assembly with thin and ultra thin Chips (20 –150 μm)

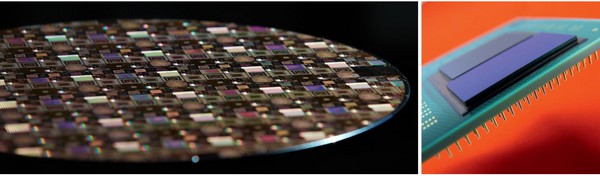

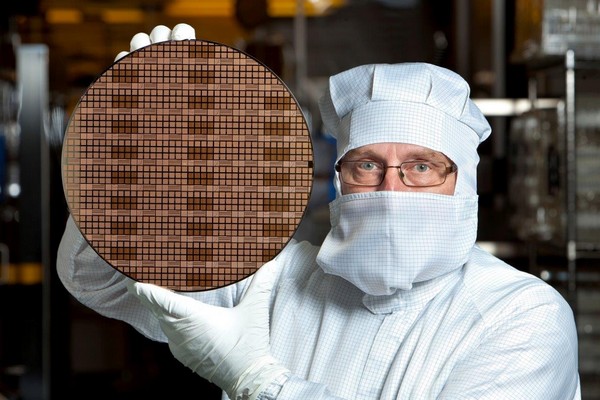

Das Center »All Silicon System Integration Center Dresden« (ASSID) des Fraunhofer IZM wurde im Jahre 2010 eröffnet und ist integrierter Bestandteil der Wafer-Level-Packaging- und Systemintegration-Aktivitäten des Fraunhofer IZM. Das Fraunhofer IZM-ASSID verfügt über eine dem neusten Stand der Technik entsprechende, hochmoderne 300 mm-Technologielinie für die 3D-Wafer-Level-Systemintegration auf der Basis der Kupfer-Through-Silicon-Via (Cu-TSV)-Technologie. Bestandteile der Linie sind sowohl einzelne Prozessmodule für die TSV-Formierung, für das Post-TSV-Processing sowie das Vereinzeln, das Assembly und die 3D Stack Formierung. Die Konzeption der Linie erlaubt sowohl eine anwendungsbezogene Entwicklung von Prozessen als auch die Qualifikation und Prototypenfertigung für 3D-Wafer-Level-System in z.B. Packages und CSPs.

Das IZM-ASSID ist eingebunden in das Netzwerk des SiliconSaxony e.V. und kooperiert auf dem Gebiet der 3D-Integration sehr eng mit Anwendern, Anlagenherstellern und Materialzulieferern sowie unterschiedlichen Organisationen, Netzwerken und Clustern (u. a. ITRS, Sematech, Semi, IEEE). Darüber hinaus bestehen enge Kooperationen mit Fraunhofer-Instituten und anderen wissenschaftlich-technischen Einrichtungen im Freistaat Sachsen.

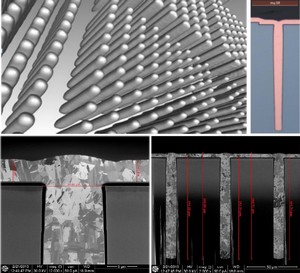

Through Silicon Via (TSV) Formation

- High-density TSV technology for advanced system performance

- Via-middle/Via-last process integration

- Cu-TSV filling using high-speed ECD

- TSV post processing on wafer front and back side

- Evaluation und validation of new materials for TSV filling and isolation

- High yield TSV process integration

TSV Interposer with high-density Multi-Layer Metallization

- Silicon Interposer with high-density Cu-TSV

- Both sided high-density multi layer Cu-wiring

- Integration of active and passive devices

- Compatible interconnects for 3D stacking of silicon components for wafer level assembly (D2W, W2W) and package/board-assembly